As part of my continuing efforts to understand direct memory access (DMA) capabilities of various 80’s home computer systems, I decided I should figure out what, if any, DMA capabilities are possible on the TANDY Color Computer systems. There are 3 essential models in the lineup, though from a technical perspective, I feel there are 2 main variants: The CoCo1 and 2, which share very similar features and capabilities (mainly, the difference is in some cost reduced circuitry in the 2 and more memory in the later machines) and the CoCo3, which contains a more capable video processor, substantially more memory, and a memory management unit (MMU). Most folks also consider the Dragon Data Dragon machines as part of this lineup, and those are roughly similar to the CoCo1/2 systems (both systems seem to be based on a Motorola reference design. The CP1400 might also qualify, but I don’t have one and know little about the design, so I will consider the 4 above machines inclusively

A pre-requisite for DMA operation is an ability to stop the running CPU in some fashion and a way to access internal memory and/or IO from the cartridge or expansion port. The VIC-20, for example, has no way to stop the running CPU, so DMA is not possible. However, TANDY (and Dragon Data) helpfully provided a pin on the expansion port that will temporarily shut off the internal Motorola M6809E CPU and remove its address and data signals from the system bus (this part is essential, because if the CPU is not running but it still outputs address and data on the system bus, the bus is not available for other users). On the M6809E, that signal is called !HALT and is active low. To “halt” the 6809 CPU, simply bring this line low on the expansion port during a cycle. Of course, nothing is that simple, so here’s some more detail:

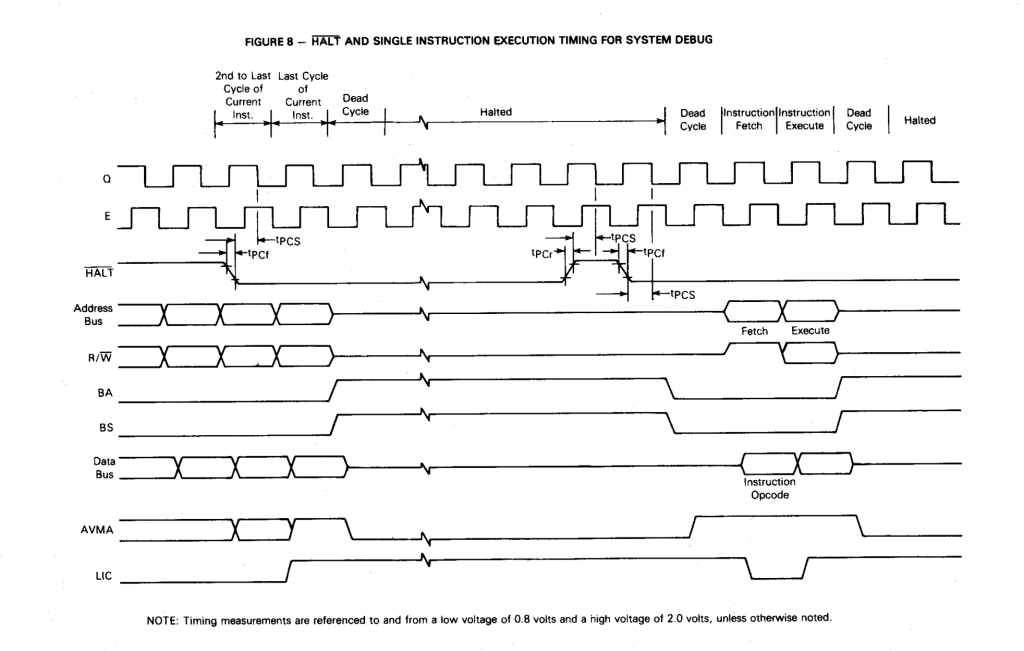

!HALT can be pulled low anytime, but will only take effect if it falls 200nS or more before the falling edge of Q (Q is 1 half of the 4 phase clock system used by the 6809 and typically is high during the middle of the CPU clock “cycle”). This consideration is called tPCS on the timing diagram, and is 200nS for a 1MHz CPU, 140nS for a 1.5MHz, and 100nS for a 2MHz CPU. As well, one can bring !HALT high at a later time, but it again must occur tPCS nS before the fall of the Q clock signal. Still, if one adheres to those rules, the entire address and data bus (on the CoCo1 and 2, anyway) is available at the expansion port for reading from and writing data to the internal memory.

One must crawl, then walk, and then run in these efforts, so the first thought is to figure out the !HALT signalling and attempt to transfer a single value from the expansion port to an internal memory location. Testing would then involve setting the internal memory location to a value other than the one expected, triggering the DMA functionality, and then looking at the internal memory location. If the value has been changed, one can be confident a DMA transfer has occurred. Once that is in place, it can be used as a foundation to expand the functionality to support the transfer of many data values to many locations, and then digress into the various useful DMA use cases (fast floppy emulator, extra memory on demand, feeding audio data to a DAC, etc.). But, it’s a tall order to transfer that first byte, so let’s focus on the task at hand.

Many years ago, I would approach this by grabbing a perfboard and wiring up some 74LS TTL logic ICs on the board to approximate the functionality desired. Of course, it would be wrong, so many hours of rewiring and soldering up new ICs would be involved. Now, though, as much as some retro enthusiasts object, I utilize a suitable Complex Programmable Logic Device (CPLD) attached to a small cartridge PCB to efficiently design the required logic. While soldering and deciding on the correct TTL IC has value, if you’re trying to make something work, those activities can get in the way of the design process. A CPLD allows one to change the design simply by modifying the “software”, downloading it into the IC, and testing. Once the design is working, one can translate back into TTL ICs if desired, or (in many of my recent designs), simply continue to utilize a CPLD. CPLDs are the children of PLDs like the 16v8 PAL used in the 1980’s, and some CPLD variants were available in the era of these machines. These complex devices can replace dozens of ICs in a design, decreasing finished unit costs consderibly and bringing these types of functions well within the grasp of hobbyists to manufacture and enthusiasts to buy. Since I’ve always desired to create economical solutions for these classic machines, the CPLD provides significant value. Still, for the moment, I’m most interested in the design efficiencies, especially since there’s no guarantee anything will work in the end.

One thought on “Direct Memory Access Possibilities on the TANDY Color Computer”

Comments are closed.